架构-计算机基础1-硬件

概述

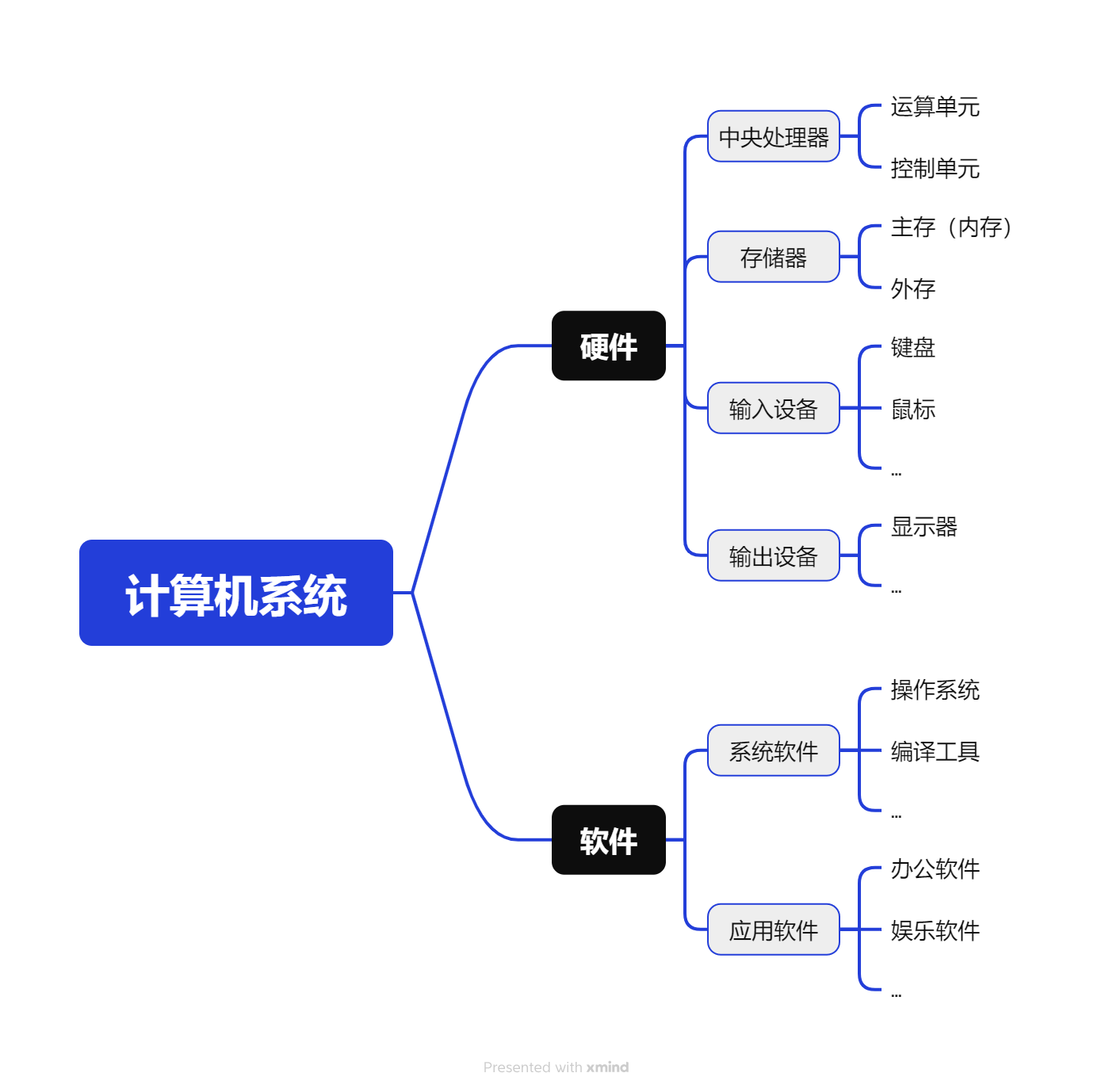

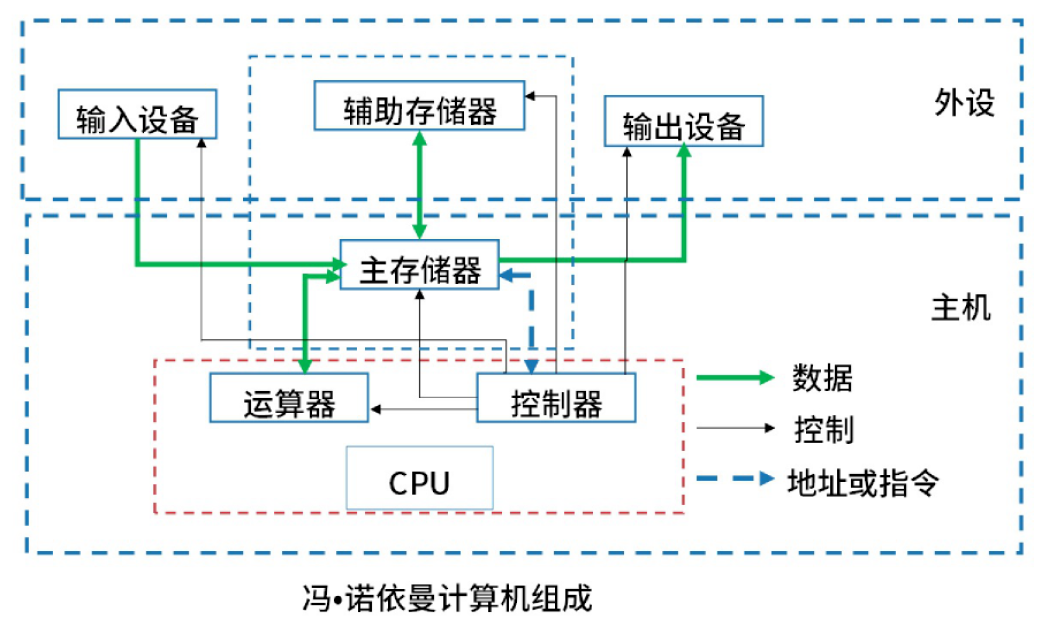

冯诺依曼结构,整体结构可如图

- 运算器

- 控制器

- 存储器

- 输入设备

- 输出设备

处理器

运算器和控制器是处理器的核心部件

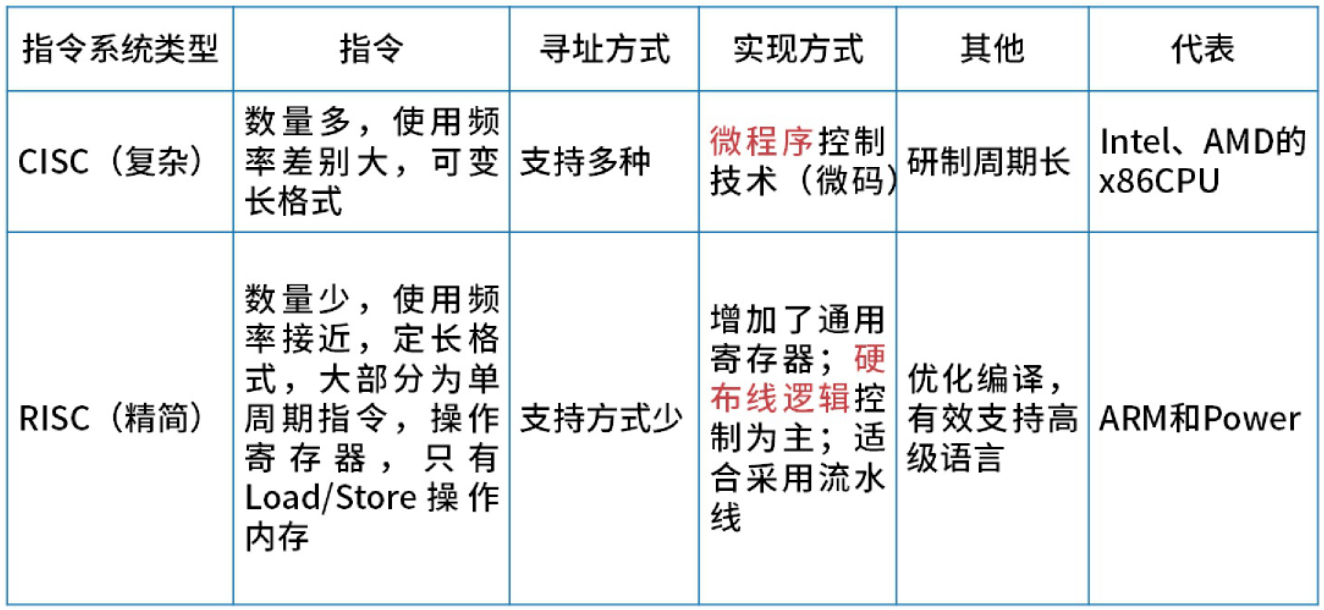

指令集:复杂指令集CISC、精简指令集RISC

常见处理芯片:图形处理器GPU,信号处理器DSP,可编程逻辑门阵列FPGA等

存储

存储器:用于存储数据的电子设备。

按硬件接口分分:

- SRAM

- DRAM

- NVRAM

- Flash

- EPROM

- Disk

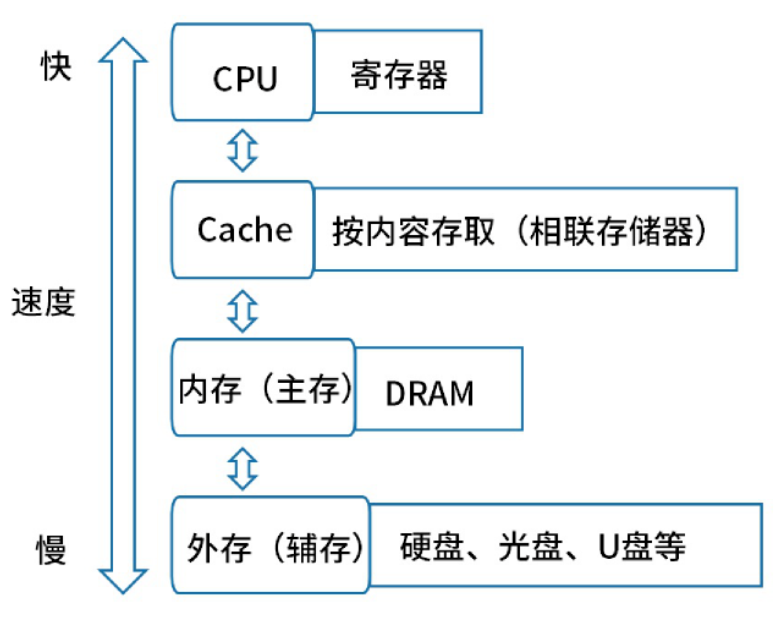

按与处理器的物理距离分:

- 片上缓存:在处理器核心中,一般为SRAM,快速读取,容量小,16kB-512kB,可分一级或二级

- 片外缓存:在处理器核心外,需要交换互联开关,一般SRAM,256kB-4MB,称为L2Cache或L3Cache,平台Cache

- 主存(内存):DRAM,独立部件/芯片,通过总线与处理器连接。需要持续供电,数百MB-数十GB

- 外存:磁带、磁盘、Flash等,速度慢、容量大、掉电仍保存数据

SRAM、DRAM掉电数据丢失。SRAM读取10-20ns,直接通过晶体管状态,面积大,成本高;DRAM读取50ns,通过充放电

时间局限性:指程序中某条指令一旦执行,不久以后该指令可能再次执行,典型原因是由于程序中存在大量的循环操作

空间局限性:指一旦程序访问了某个存储单元,不久之后,其附近的存储单元也将被访问,即程序在一段时间内所访问的地址可能集中在一定范围内,其典型情况是程序顺序执行

总线

总线:计算机内部间遵循某一特定协议实现数据交互的形式。总线之间通过【桥】实现连接,它是一种特殊的外设,主要实现总线协议间的转换

- 内总线:用于芯片内部互联,又称片上总线、片内总线

- 系统总线:包括 数据总线、地址总线和控制总线

- 狭义上:CPU、主存、IO接口的总线

- 广义上:经由系统总线再次级联的总线,常称为局部总线

- 外部总线:计算机板和外部设备,计算机系统之间互联的总线,又称通信总线

性能指标

- 总线带宽

- 总线服务质量QoS

- 总线时延

- 总线抖动

类型

- 并行总线:PCI、PCIe和ATA(IDE)

- 串行总线:USB、SATA、CAN、RS-232、RS-485、RapidIO和以太网

接口

接口是同一计算机不同功能层之间的通信规则

- 显示类接口:HDMI、DVI、VGA

- 音频输入输出类接口:TRS、RCA、XLR

- 网络类接口:RJ45、FC

- PS/2接口

- USB接口

- SATA接口

- LPT打印接口

- RS-232接口

对于总线而言,一种总线可能存在多种接口

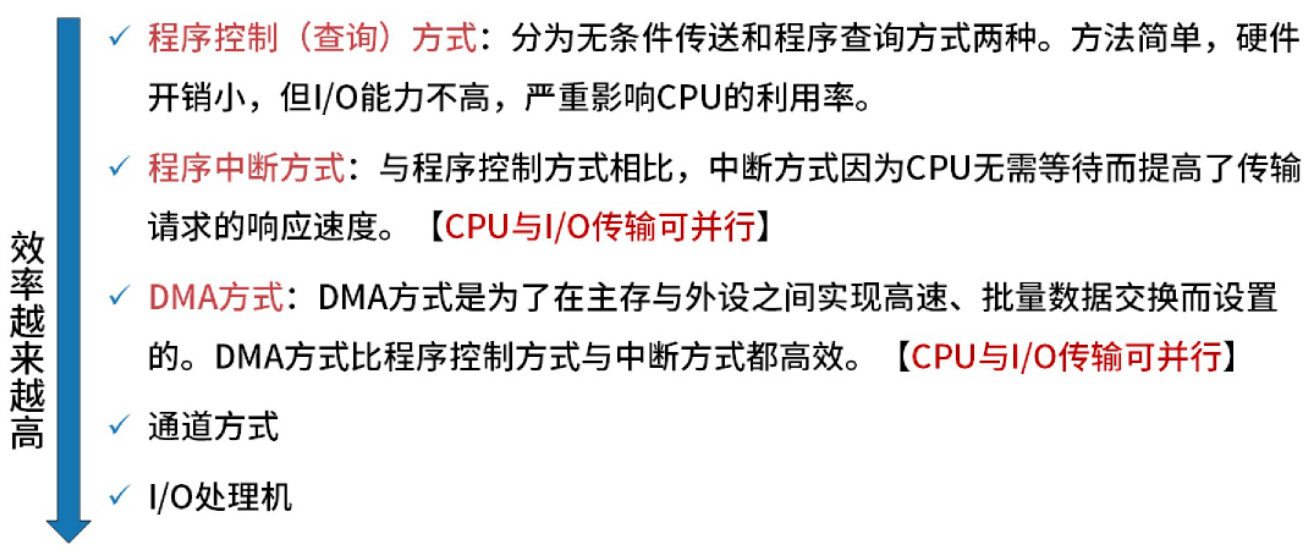

直接主存存取(Direct Memory Access,DMA)是指数据在主存与I/O设备间的直接成块传送,即在主存与I/O设备间传送数据块的过程中,不需要CPU作任何干涉,只需在过程开始启动(即向设备 发出“传送一块数据”的命令)与过程结束(CPU通过轮询或中断得知过程是否结束和下次操作是否准备就绪)时由CPU进行处理,实际操作由DMA硬件直接完成,CPU在传送过程中可做其它事情。

架构-计算机基础1-硬件

http://060800.xyz/2025/07/17/架构/架构-计算机基础1-硬件/